## **BRIEF DATASHEET**

PART NUMBER: CT4948A21962D1

DESCRIPTION: NAND FLASH 2Gb (x8)+

DDR3(L) SDRAM 4Gb (x32)

## ChipSiP Technology Co., Ltd.

8F-1, No. 186, Jian 1st Rd, Zhonghe District, New Taipei City 235, Taiwan Tel: 886-2-8227-1799 Fax: 886-2-8227-1798

E-mail: sales@ChipSiP.com www.ChipSiP.com

#### Combo Memory (Green MCP)

2G bits (256M x 8-bit) NAND Flash Memory + 4G bits (16M x 8-Bank x 32-bit) DDR3(L) SDRAM

## Copyright

© 2016 ChipSiP Technology Co., Ltd. All rights reserved. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means without written permission of ChipSiP Technology Co., Ltd.

#### **Disclaimer**

ChipSiP provides this document "as is", without warranty of any kind. ChipSiP may make improvements and/or changes in this document or in the product described in this document at any time. This document could include technical inaccuracies or typographical errors.

#### **Trademarks**

ChipSiP is a trademark of ChipSiP Technology Co., Ltd. Other names mentioned in this document are trademarks/registered trademarks of their respective owners.

## **Using This Document**

This document is intended for hardware and software engineer's general information on the CT4948A21962D1 .Though every effort has been made to ensure that this document is current and accurate, more information may have become available subsequent to the production of this guide.

## **Revision History**

| Revision | Date       | Description                                 |

|----------|------------|---------------------------------------------|

| Rev 0.1  | 2016/06/14 | Create new document                         |

| Rev 0.2  | 2016/09/05 | Modified 1.2 Features:NAND FLASH Block size |

#### **Combo Memory (Green MCP)**

2G bits (256M x 8-bit) NAND Flash Memory + 4G bits (16M x 8-Bank x 32-bit) DDR3(L) SDRAM

#### 1. INTRODUCTION

CT4948A21962D1 is a Multi Chip Package Memory (MCP) that integrated 2G bits NAND Flash and 2G bits DDR3(L) SDRAM x2 by advanced SiP (System-in-a-Package) technology. CT4948A21962D1 offers space saving advantage that could miniaturize your portable device, and it is conformed with Green regulations.

## 1.1 Application

- Compact DSC / CAR Black Box / Action Cam / 360 Cam

- Drone

- Wearable

#### 1.2 Features

#### **PRODUCT LIST**

- CT4948A21962D1

- NAND FLASH: 2G bits (256M x 8-bit)

- DDR3(L) SDRAM: 4G bits (16M x 8-Bank x32-bit)

#### **POWER SUPPLY**

- NAND FLASH

- ■2.7-3.6V

- DDR3(L) SDRAM

- ■DDR3L: 1.35V (1.283–1.45V) / Backward-compatible to DDR3: 1.5V ±0.075V

#### **PACKAGE**

- •FBGA 10.5 x 13.5 x 1.4mm, 148 Balls

- •Ball Pitch: 0.8 mm

- •Weight: 332mg +/-5mg

#### **Temperature**

- Operating: -10 to +85 °C

- Storage: -55 to +125°C

#### **Combo Memory (Green MCP)**

2G bits (256M x 8-bit) NAND Flash Memory + 4G bits (16M x 8-Bank x 32-bit) DDR3(L) SDRAM

#### **NAND FLASH**

- Density

- ■2Gbit

- Architectur

- Single-level Cell(SLC) Technology

- OPEN NAND FLASH INTERFACE(ONFI)1.0 COMPLIANT

- POWER SUPPLY VOLTAGE

- ■VCC = 2.7V ~ 3.6V

- MEMORY CELL ARRAY (with SPARE)

- Page size

X8: (2K+128spare) bytes

■Block size

X8: (128K+8K) bytes

■ Plane size: 1024blocks

■ Device size : 2048blocks

- PAGE READ / PROGRAM

- Random Read Time(tR): 30us(Max)

- Sequential access time

- 3.3V Device:25ns(Min)

- Page program

3.3V Device: 300us(Typ)

■ Multi-page program(2 pages)

3.3V Device: 300us(Typ)

- BLOCK ERASE

- Block erase time: 3.5ms(Typ)

- Multi-block erase(2 Blocks)

- 3.3V Device: 3.5ms(Typ)

- COMMAND SET

- ONFI1.0 Compliant command set

- Read Unique ID

- SECURITY

- OTP area

- Serial number(unique ID)

- Non-volatile protection

- ELECTRONIC SIGNATURE

- 1<sup>st</sup> cycle: Manufacturer Code

- 2<sup>nd</sup> cycle: Device Code

#### **Combo Memory (Green MCP)**

2G bits (256M x 8-bit) NAND Flash Memory + 4G bits (16M x 8-Bank x 32-bit) DDR3(L) SDRAM

■ 3<sup>rd</sup> cycle: Internal chip number, Cell Type, Number of

Simultaneously Programmed Pages,

Interleaved Program, Write Cache

■ 4<sup>th</sup> cycle: Page size, Block size, Organization,

Spare size, Serial Access Time

- 5<sup>th</sup> cycle: ECC, Multi-plane information

- RELIABILITY

- 50,000 Program / Erase cycles (with 4bit/512 ECC)

- DATA RETENTION

- 10 years

#### DDR3(L) SDRAM

- DDR3L: VDD = VDDQ = 1.35V (1.283–1.45V)

- Backward-compatible to DDR3: VDD = VDDQ = 1.5V ±0.075V

- Differential bidirectional data strobe

- 8*n*-bit prefetch architecture

- Differential clock inputs (CK, CK#)

- 8 internal banks

- Nominal and dynamic on-die termination (ODT) for data, strobe, and mask signals

- Programmable CAS READ latency (CL)

- Posted CAS additive latency (AL)

- Programmable CAS WRITE latency (CWL) based on tCK

- Fixed burst length (BL) of 8 and burst chop (BC) of 4 (via the mode register set [MRS])

- Selectable BC4 or BL8 on-the-fly (OTF)

- Self refresh mode

- Tc of -10°C to 95°C

- 64ms, 8192 cycle refresh at -10°C to 85°C

- 32ms, 8192 cycle refresh at 85°C to 95°C

- Self refresh temperature (SRT)

- Write leveling

- Multipurpose register

- Output driver calibration

- Page size

- 2KB

- DDR3L: only for 1.35V parameters, setting, or description

- DDR3: only for 1.5V parameters, setting, or description

- DDR3(L): both of them can use the same parameters, setting, or description

## **Combo Memory (Green MCP)**

2G bits (256M x 8-bit) NAND Flash Memory + 4G bits (16M x 8-Bank x 32-bit) DDR3(L) SDRAM

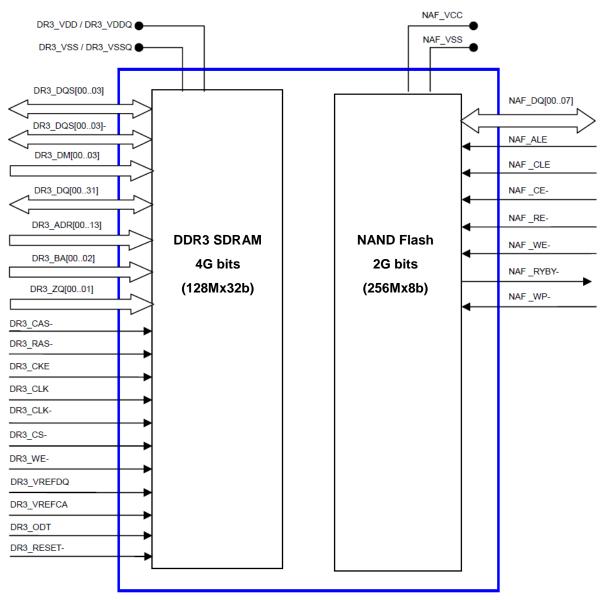

# 2. FUNCTION DIAGRAM 2.1 MCP

2G bits (256M x 8-bit) NAND Flash Memory + 4G bits (16M x 8-Bank x 32-bit) DDR3(L) SDRAM

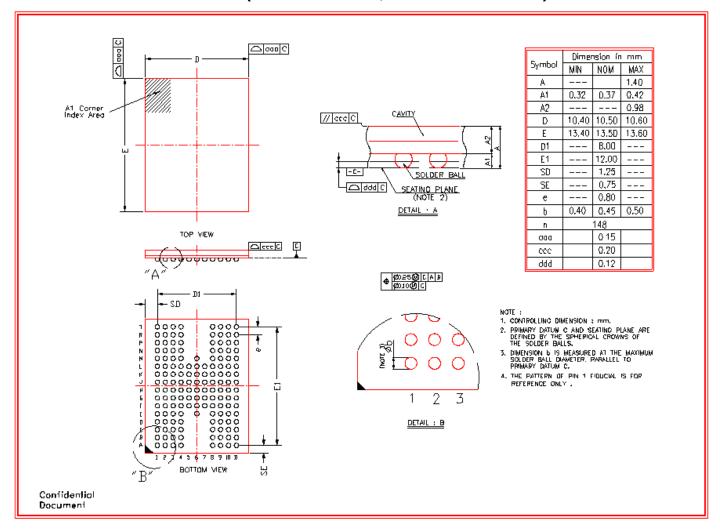

## 3. PACKAGE DIMENSION (148 Ball FBGA, 10.5x13.5x1.4mm)